# A 1.8~3.2-GHz Fully Differential GaAs MESFET PLL

Tae-Sik Cheung, Member, IEEE, Bhum-Cheol Lee, Eun-Chang Choi, and Woo-Young Choi, Member, IEEE

Abstract—A 1.8 ~ 3.2-GHz fully differential phase-locked loop (PLL) is realized for asynchronous transfer mode clock generation applications. The PLL includes a new differential voltage controlled oscillator with the wide tuning range of 1.74 ~ 3.40 GHz and a new differential charge pump with improved hold characteristics. The PLL is implemented with 0.5- $\mu$ m GaAs MESFET technology. The experimental results show that the proposed PLL has a lock range of 1.8 ~ 3.2 GHz and its output RMS jitter is at most 5.0 ps (0.015 UI) at 3.2 GHz.

*Index Terms*—MESFET integrated circuits, phase-locked loops, very-high-speed integrated circuits.

### I. INTRODUCTION

N MULTILINK systems such as asynchronous transfer mode (ATM), it is cost effective to integrate several links into one high-speed serial link reducing the system complexity. This requires high-speed phase-locked loops (PLLs) which provide the system clock for data serialization and deserialization. There have been intensive research efforts to increase the operating frequency and operating range of the PLL, and reduce output jitter [1]–[9]. Most research efforts for high-speed PLL are focused on the voltage controlled oscillator (VCO) and the charge pump, since the maximum operating frequency and operating range of the PLL are determined by the VCO and the jitter characteristics are influenced by the VCO and the charge pump. Our goal is realizing a high-speed PLL with a wide lock range and low jitter characteristics for ATM applications. In order to achieve this goal, we implement new circuit ideas for the VCO and the charge pump.

# II. VOLTAGE CONTROLLED OSCILLATOR

A ring-oscillator-type VCO is widely used for PLLs for system clock generation applications, since it occupies a small chip area and produces high-frequency signals with large magnitude suitable for digital systems. Among various methods of controlling the oscillation frequency ( $f_{\rm OSC}$ ) of the ring-oscillator-type VCO [10]–[12], the feedback loop

B.-C. Lee and E.-C. Choi are with the Switching Technology Department, Electronics and Telecommunications Research Institute, Taejon 305-350, Korea.

W.-Y. Choi is with the Department of Electrical and Electronic Engineering, Yonsei University, Seoul 120-749, Korea (e-mail: wchoi@yonsei.ac.kr).

Publisher Item Identifier S 0018-9200(01)02407-6.

$t_{d}$   $t_{d$

AMUX

Fig. 1. Block diagram of the conventional VCO using feedback loop coupling.

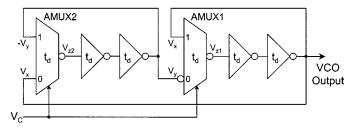

Fig. 2. Block diagram of the proposed VCO.

coupling method [12] is most suitable for the high-speed PLL application. This is because it can be designed with a fully differential structure, it has no maximum oscillation frequency degradation due to output loading capacitance, and with it the VCO tuning range can be easily determined.

Fig. 1 shows the block diagram of a conventional VCO using the feedback loop coupling method. The  $f_{OSC}$  is controlled by the control signal ( $V_C$ ) of an analog multiplexer (AMUX) which combines two loops having different loop delays. By assuming that the propagation delays for the inverters and AMUX are  $t_d$ , the VCO tuning range can be determined as  $1/(10t_d) \sim 1/(6t_d)$ [12].

Although this type of VCO has several advantages, as mentioned above, there is a limitation in increasing its tuning range due to the unstability of the AMUX. In Fig. 1, the delay time difference between two AMUX inputs is  $2t_d$ . When the VCO oscillates with its minimum oscillation frequency, the oscillation period of the VCO is  $10t_d$ , and the phase difference between two AMUX inputs is  $2\pi/5$ . Similarly, when it oscillates with its maximum oscillation frequency, the phase difference of two AMUX inputs is  $2\pi/3$ . Therefore, the AMUX input phase difference is in the range of  $2\pi/5 \sim 2\pi/3$ . This can make the VCO loop gain too small so that the oscillation is ceased, because as the AMUX input phase difference increases, the magnitude of the AMUX output decreases [13].

Fig. 2 shows the block diagram of a new VCO structure [13], [14] realized in this paper. It has two identical loops, each of which consists of one AMUX and several inverters. One loop together with the AMUX of the other loop acts as a variable

Manuscript received May 3, 2000; revised December 6, 2000. This work was supported by the Korean Ministry of Information and Communications and by the Brain Korea 21 Project.

T.-S. Cheung was with the Department of Electrical and Electronic Engineering, Yonsei University, Seoul 120-749, Korea. He is now with the Switching Technology Department, Electronics and Telecommunications Research Institute, Taejon 305-350, Korea.

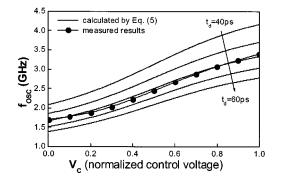

Fig. 3. Measured and calculated VCO tuning sensitivity.

delay element of the other loop. Since two loops are combined by AMUXs, voltage signals appeared in all nodes of the VCO always have the same frequency,  $f_{OSC}$ . Consequently, the operation of the VCO shown in Fig. 2 can be explained by a simple phasor analysis as in the case of the VCO shown in Fig. 1. Assuming that the AMUX output  $V_z$  is linearly controlled by  $V_C$ which varies from 0 to 1 and the propagation delays of AMUXs and inverters are  $t_d$ , the following relationship can be derived:

$$V_{z1} = [(1 - V_{\rm C})V_y + V_{\rm C}V_x] \cdot e^{-j\theta}$$

$$V_{z2} = [(1 - V_{\rm C})V_x - V_{\rm C}V_y] \cdot e^{-j\theta}$$

(1)

$$V_x = -A^2 e^{-j2\theta} V_{z1}$$

and  $V_y = A^2 e^{-j2\theta} V_{z2}$  (2)

where A is the small signal gain of the inverter at the frequency of  $f_{OSC}$ , and  $\theta$  is the output phase delay produced by the inverter and AMUX. From (1) and (2), the relationship between  $V_{z1}$  and  $V_{z2}$  is obtained as

$V_{z1} = \frac{(1 - V_{\rm C})A^2 e^{-j3\theta}}{1 + V_{\rm C}A^2 e^{-j3\theta}} \cdot V_{z2}$

and

$$V_{z2} = -\frac{(1 - V_{\rm C})A^2 e^{-j3\theta}}{1 + V_{\rm C}A^2 e^{-j3\theta}} \cdot V_{z1}.$$

(3)

From (3),  $e^{-j3\theta}$  can be derived as

$$e^{-j3\theta} = -jA^{-2} \left[ (1 - V_{\rm C}) + jV_{\rm C} \right]^{-1}$$

(4)

Since  $\theta$  can be expressed as  $\theta = 2\pi t_d/T_{OSC}$ ,  $f_{OSC}$  is derived from (4) as

$$f_{\rm OSC} = \frac{1}{2\pi} \cdot \left[\frac{\pi}{2} + \tan^{-1}\left(\frac{V_{\rm C}}{1 - V_{\rm C}}\right)\right] \cdot \frac{1}{3t_d}.$$

(5)

From (5), it can be seen that the new VCO has the tuning range of  $1/(12t_d) \sim 1/(6t_d)$ , which is wider than that of the conventional VCO structure.

Fig. 3 shows the experimental results in which the tuning range of the proposed VCO is analyzed. Results calculated with (5) are also shown. The VCO is implemented fully differentially by using a source-coupled FET logic (SCFL) inverter [15] and a SCFL AMUX, which is shown in Fig. 4. The experimental results show that the VCO tuning range is  $1.74 \sim 3.40$  GHz and it can be accurately fitted by (5) by using  $t_d = 50$  ps.

Fig. 4. Schematic diagram of the SCFL AMUX.

The advantage of the new VCO is that the AMUX input phase difference is fixed at  $\pi/2$  in the whole tuning range. As shown in Fig. 2, two inputs of AMUX1 and AMUX2 are  $V_x$  and  $V_y$ , and  $V_y$  and  $V_x$ , respectively. In case of AMUX1, the phase difference between  $V_y$  and  $V_x$  is exactly  $\pi/2$ , because  $V_y$  is a delayed signal of  $V_x$  by  $3t_d$ , and  $V_x$  is an oscillating signal which has a period of  $12t_d$ . In case of AMUX2, the phase difference between  $V_x$  and  $V_y$  is also exactly  $\pi/2$ , because the phase difference between  $V_x$  and  $V_y$  is  $\pi$ .

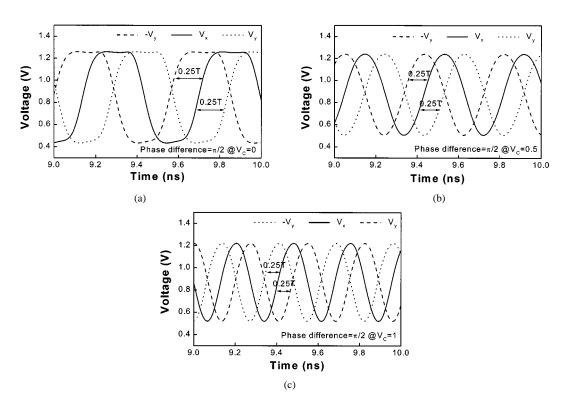

Fig. 5 shows the simulation results to evaluate the phase relationship between  $V_x$ ,  $V_y$ , and  $V_y$  at  $V_C = 0, 0.5$ , and 1. As shown in the figure, the phase difference between  $V_x$  and  $V_y$ , and  $V_x$  and  $-V_y$  are exactly  $\pi/2$  in the whole tuning range. This guarantees the stable operation of AMUXs.

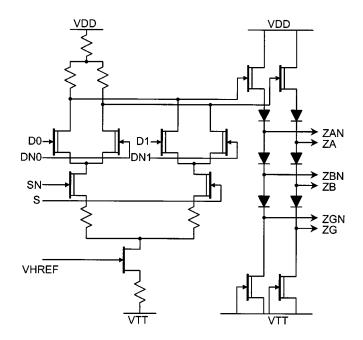

## III. CHARGE PUMP

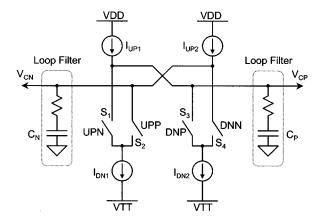

A differential charge pump is generally used for high-speed PLL applications because of its fast switching capability. Fig. 6 shows the schematic diagram of a conventional differential charge pump [6]. In this figure, UPP, UPN, DNP, and DNN are the differential outputs of PFD. When it is in the hold state (UP=DN="0"),  $I_{\rm UP1}$  flows to  $I_{\rm DN1}$  and  $I_{\rm UP2}$  to  $I_{\rm DN2}$ . If  $I_{\rm UP1}$ is exactly same as  $I_{\rm UP2}$  and  $I_{\rm DN1}$  as  $I_{\rm DN2}$ , the charge pump outputs  $V_{\rm CP}$  and  $V_{\rm CN}$  are not changed. When it is in the up state (UP="1," DN="0"),  $I_{\rm UP2}$  flows to  $I_{\rm DN2}$  and  $I_{\rm UP1}$  to the loop filter capacitor  $C_P$  increasing  $V_{\rm CP}$ , and  $I_{\rm DN1}$  flows from the loop filter capacitor  $C_N$  decreasing  $V_{\rm CN}$ . In the similar way, when it is in the down state (UP="0," DN="1"),  $V_{\rm CP}$  is decreased and  $V_{\rm CN}$  is increased.

However, as the charge pump output level is shifted from its initial bias level, it tends to converge to its initial state. This is because the current sources  $I_{\rm UP1}$  and  $I_{\rm UP2}$  have finite output resistances and  $I_{\rm UP1}$  and  $I_{\rm UP2}$  are proportional to the charge pump output voltages,  $V_{\rm CP}$  and  $V_{\rm CN}$ , respectively. This problem is particularly serious for GaAs MESFET circuits as there is no

Fig. 5. Phase relationship between two AMUX inputs as a function of  $V_{\rm C}$ . (a)  $V_{\rm C} = 0.$  (b)  $V_{\rm C} = 0.5$ . (c)  $V_{\rm C} = 1$ .

Fig. 6. Schematic diagram of the conventional charge pump.

complementary FET and consequently it is very difficult to design proper current sources. In [16], a differential charge pump was proposed to lessen this problem by controlling  $I_{\rm DN1}$  and  $I_{\rm DN2}$  with the charge pump output. However, this is not a perfect solution, as it is difficult to exactly match  $I_{\rm DN1}$  to  $I_{\rm UP1}$  and  $I_{\rm DN2}$  to  $I_{\rm UP2}$ .

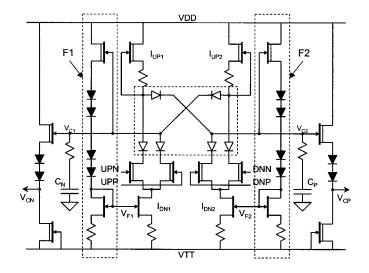

Fig. 7 shows the schematic diagram for our new charge pump [13], [17]. Six diodes are placed in each current path to prevent the charges in the loop filter capacitors from flowing to the current sinks during the hold state. In order to block the leakage currents from  $I_{\rm UP1}$  and  $I_{\rm UP2}$  to  $C_P$  and  $C_N$ , the current sink control blocks, F1 and F2, are implemented which respectively make  $I_{\rm DN1}$  and  $I_{\rm DN2}$  to be equal to or larger than  $I_{\rm UP1}$  and  $I_{\rm UP2}$ . This scheme differs from the current sink control method used in [16] in that  $I_{\rm DN1}$  and  $I_{\rm DN2}$  do not have to be exactly matched to  $I_{\rm UP1}$  and  $I_{\rm UP2}$ . The only requirement in our scheme

Fig. 7. Schematic diagram of the proposed charge pump.

is  $I_{\text{DN1}} \ge I_{\text{UP1}}$  and  $I_{\text{DN2}} \ge I_{\text{UP2}}$ , a much easier condition to satisfy.

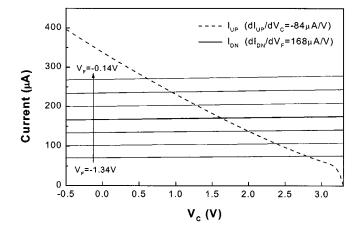

Fig. 8 shows the simulation results to evaluate the dependence of  $I_{\rm UP}$  and  $I_{\rm DN}$  on charge pump output  $V_{\rm C}$ . As shown in the figure,  $I_{\rm UP}$  is linearly proportional to  $V_{\rm C}$  with the slope of -84  $\mu$ A/V. But  $I_{\rm DN}$  is nearly independent of  $V_{\rm C}$  while it is linearly proportional to the current sink control voltage  $V_F$ with the slope of 168  $\mu$ A/V. From this, it can be determined that the current sink control blocks F1 and F2 have the voltage gain,  $dV_F/dV_{\rm C}$ , larger than 0.5 satisfying  $I_{\rm DN} \ge I_{\rm UP}$ . Consequently, a source follower with the small signal gain of 1 can be used for F1 and F2.

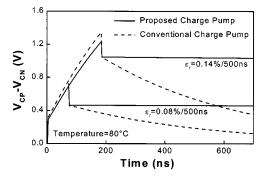

Fig. 9 shows the simulation results for the output hold characteristics of the proposed and the conventional charge pump.

Fig. 8. Dependence of  $I_{\rm UP}$  and  $I_{\rm DN}$ , on  $V_{\rm C}$  and  $V_F$ .

Fig. 9. Comparison of output hold characteristics for the proposed and the conventional charge pumps.

In the conventional charge pump, it converges to its initial state as the output level goes up from its initial bias level. In comparison, the output level in the new charge pump keeps its level during the hold state. The maximum relative drift of output level of the proposed charge pump output is 0.14% during 500 ns.

### **IV. EXPERIMENTAL RESULTS**

A PLL that has the newly proposed VCO and charge pump was implemented with 0.5- $\mu$ m GaAs MESFET technology. Although it is possible to implement gigahertz-range PLLs with 3-V CMOS technology, we have chosen the GaAs MESFET process technology for application because this work is a part of very-high-speed ATM switch implementation based on MESFET. Fig. 10 shows the layout of the chip, which includes three PLLs with slight modifications for measurement purposes. The PLL uses a generic PFD implemented with eleven OR/NOR gates, a programmable frequency divider implemented with a 4-bit counter and several combinational logics, and on-chip second-order loop filters. The loop filter parameters  $(1800 \Omega, 40 \text{ pF}, 4 \text{ pF})$  were chosen to make the damping factor  $(\zeta)$  of the closed-loop transfer function to be 0.707, which corresponds to the loop bandwidth of 6.45 MHz when the dividing number is set to 20. The power dissipation for the PLL core is estimated to be 380 mW with +3.3-V/-2.0-V power supplies. This high power consumption is due to the fact that all PLL core blocks are designed fully differentially and the programmable frequency divider has many SCFL flip-flops and

Fig. 10. Layout of PLL. (Three PLL circuits are included.)

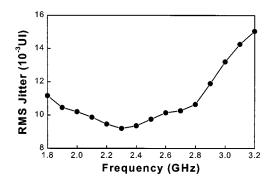

Fig. 11. Measured jitter characteristics of the fabricated PLL.

combinational logics. We estimate that the power dissipation for frequency divider alone is 210 mW. One possible way of reducing power dissipation would be using single logics such as direct-coupled FET logic (DCFL) where possible.

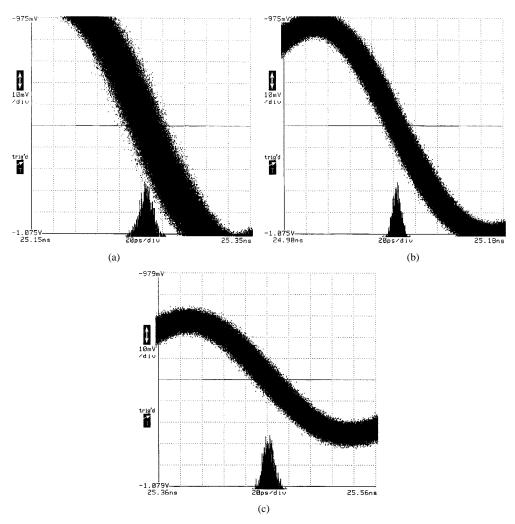

The PLL was fully functional with a lock range of  $1.8 \sim 3.2$  GHz with the input reference signal ranging from 90 to 160 MHz. Fig. 11 shows the measured RMS jitters for the entire lock ranges. The jitter ranges from 0.009 UI at about the center oscillation frequency to 0.015 UI at the highest oscillation frequency. Fig. 12 shows the measured jitter histograms of the VCO output when the PLL was locked at its minimum, center, and maximum frequency. The RMS jitters for the VCO output are 6.2 ps (0.011 UI) at  $f_{\rm VCO} = 1.8$  GHz, 3.9 ps (0.010 UI) at  $f_{\rm VCO} = 2.6$  GHz, and 5.0 ps (0.015 UI) at  $f_{\rm VCO} = 3.20$  GHz.

# V. CONCLUSION

A  $1.8 \sim 3.2$ -GHz fully differential on-chip PLL was successfully realized with 0.5- $\mu$ m GaAs MESFET process technology. This PLL includes a newly proposed VCO which has an enhanced tuning range and stability, and a newly proposed differential charge pump which has improved output hold characteristics. The experimental results show that the PLL has a lock range of  $1.8 \sim 3.2$  GHz and the maximum VCO RMS jitter of 5.0 ps (0.015 UI) at 3.2 GHz. It is believed that our PLL can find very useful applications for high-speed clock generation systems.

Fig. 12. Measured jitter histograms of VCO output. (a)  $f_{\rm VCO} = 1.8$  GHz. (b)  $f_{\rm VCO} = 2.6$  GHz. (c)  $f_{\rm VCO} = 3.2$  GHz.

# REFERENCES

- J. T. Wu and R. C. Walker, "A bipolar 1.5-Gb/s monolithic phase-locked loop for clock and data extraction," in *Dig. Tech. Papers Symp. VLSI Circuits*, 1992, pp. 70–71.

- [2] B. Razavi and J. Sung, "A 6-GHz 60-mW BiCMOS phase-locked loop with 2-V supply," in *Dig. Tech. Papers IEEE Int. Solid-State Circuits Conf.*, 1994, pp. 114–115.

- [3] W. Baumberger and M. L. Schmatz, "A GaAs single-chip 2.4-GHz PLL frequency multiplier," in *Dig. Tech. Papers IEEE Microwave and Millimeter-Wave Monolithic Circuits Symp.*, 1996, pp. 39–42.

- [4] B. Razavi, "A 2-GHz 1.6-mW phase-locked loop," in Dig. Tech. Papers 1996 Symp. VLSI Circuits, 1996, pp. 26–27.

- [5] S. Nati and I. Kyles, "A monolithic gallium arsenide interval timer IC with integrated PLL clock synthesis having 500-ps single-shot resolution," *IEEE J. Solid-State Circuits*, vol. 32, pp. 1350–1356, Sept. 1997.

- [6] W. Lin and W. C. Black, "A low jitter 1.25-GHz CMOS analog PLL for clock recovery," in *Proc. IEEE Int. Symp. Circuits and Systems*, vol. 1, 1998, pp. 167–170.

- [7] W. Z. Chen and J. T. Wu, "A 2-V 1.6-GHz BJT phase-locked loop," in Proc. IEEE Custom Integrated Circuits Conf., 1998, pp. 563–566.

- [8] W. G. Lee, "Design of low-jitter 1-GHz phase-locked loops for digital clock generation," in *Proc. IEEE Int. Symp. Circuits and Systems*, vol. 2, 1999, pp. 520–523.

- [9] J. H. Song, T. W. Yoo, J. H. Ko, C. S. Park, and J. K. Kim, "Design and characterization of 10-Gb/s clock and data recovery circuit implemented with phase-locked loop," *ETRI Journal*, vol. 21, no. 3, pp. 1–5, 1999.

- [10] K. E. Syed and A. A. Abidi, "Gigahertz voltage-controlled ring oscillator," *Electron. Lett.*, vol. 22, pp. 677–679, Dec. 1986.

- [11] D. L. Campbell, "Interruptable voltage controlled oscillator and phaselocked loop using same," U.S. Patent 4 565 976, Aug. 5, 1983.

- [12] R. C. Walker, "Fully integrated high-speed voltage controlled ring oscillator," U.S. Patent 4 884 041, Nov. 28, 1989.

- [13] T. S. Cheung, "A design of gigahertz-range GaAs MESFET phase-locked loops," Ph.D. dissertation, Yonsei Univ., Seoul, Korea, 2000.

- [14] E. C. Choi, B. C. Lee, T. S. Cheung, and W. Y. Choi, "Two-stage voltagecontrolled ring oscillator using one pair of variable delay elements," Korean Patent Pending, 99-28 262, 1999.

- [15] S. Katsu, S. Nambu, S. Shimano, and G. Kano, "A GaAs monolithic frequency divider using source coupled FET logic," *IEEE Electron Device Lett.*, vol. 3, pp. 197–199, Aug. 1982.

- [16] J. R. Wahl and R. E. Hester, "Integrated, high speed, zero hold current and delay compensated charge pump circuit," U.S. Patent 4 847 519, July 11, 1989.

- [17] B. C. Lee, E. C. Choi, T. S. Cheung, K. C. Park, and W. Y. Choi, "A high-speed charge pump circuit," Korean Patent Pending, 99-29 262, 1999.

**Tae-Sik Cheung** (S'95–M'99) received the B.S., M.S. and Ph.D. degrees, all from the Department of Electrical and Electronic Engineering, Yonsei University, Seoul, Korea.

In 2000, he joined the Switching Technology Department, Electronics and Telecommunications Research Institute (ETRI), Taejon, Korea, where he is currently a Senior Member of Engineering Staff with the high-speed switch team. His current research interest is in the area of high-speed mixedsignal circuit design including phase-locked loops

```

and data transceivers.

```

interconnection.

**Bhum-Cheol Lee** received the B.S. degree from Kyung-Hee University, Seoul, Korea, in 1981, and the M.S. and Ph.D. degrees from Yonsei University, Seoul, in 1983 and 1997, respectively.

From 1983 to 1995, he was with the Electronics and Telecommunications Research Institute (ETRI), Taejon, Korea, as an Interface, Switching, Link, and Network Synchronization Engineer. Currently he is the Project Leader of the high-speed switch team at ETRI. His research interests are synchronization, line coding, and analog and digital circuits design.

**Eun-Chang Choi** received the B.S. and M.S. degrees in electronics engineering from Kyungpook National University, Taegu, Korea, in 1990 and 1992, respectively

From 1992 to 1993, he worked for the Korea Atomic Energy Research Institute. He joined the Electronics and Telecommunications Research Institute (ETRI), Taejon, Korea, in 1994 and is currently a Senior Member of Engineering Staff with the high-speed switch team. His research interests include high-speed VLSI design, PLLs, and

**Woo-Young Choi** (S'89–M'92) received the B.S., M.S., and Ph.D. degrees, all in electrical engineering and computer science, from the Massachusetts Institute of Technology, Cambridge.

From 1994 to 1995, he was a Post-Doctoral Research Fellow with Nippon Telephone and Telegraph, Opto-Electronics Labs, where he worked on femtosecond all-optical switching devices. In 1995, he joined the Department of Electrical and Electronic Engineering, Yonsei University, Seoul, Korea, where he is currently an Associate Professor.

His research interest is in the area of high-speed information processing technology including high-speed opto-electronics and high-speed electronic circuits.